- 您现在的位置:买卖IC网 > Sheet目录3851 > PIC32MX130F064D-I/ML (Microchip Technology)IC MCU 32BIT 64KB FLASH 44-QFN

2011-2012 Microchip Technology Inc.

Preliminary

DS61168D-page 105

PIC32MX1XX/2XX

9.0

DIRECT MEMORY ACCESS

(DMA) CONTROLLER

The PIC32 Direct Memory Access (DMA) controller is a

bus master module useful for data transfers between

different devices without CPU intervention. The source

and destination of a DMA transfer can be any of the

memory mapped modules existent in the PIC32 (such

as Peripheral Bus (PBUS) devices: SPI, UART, PMP,

etc.) or memory itself.

Following are some of the key features of the DMA

controller module:

Four identical channels, each featuring:

- Auto-increment source and destination

address registers

- Source and destination pointers

- Memory to memory and memory to

peripheral transfers

Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source

and destination

Fixed priority channel arbitration

Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt)

DMA requests

- One-Shot or Auto-Repeat Block Transfer

modes

- Channel-to-channel chaining

Flexible DMA requests:

- A DMA request can be selected from any of

the peripheral interrupt sources

- Each channel can select any (appropriate)

observable interrupt as its DMA request

source

- A DMA transfer abort can be selected from

any of the peripheral interrupt sources

- Pattern (data) match transfer termination

Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external

event

- Invalid DMA address generated

DMA debug support features:

- Most recent address accessed by a DMA

channel

- Most recent DMA channel to transfer data

CRC Generation module:

- CRC module can be assigned to any of the

available channels

- CRC module is highly configurable

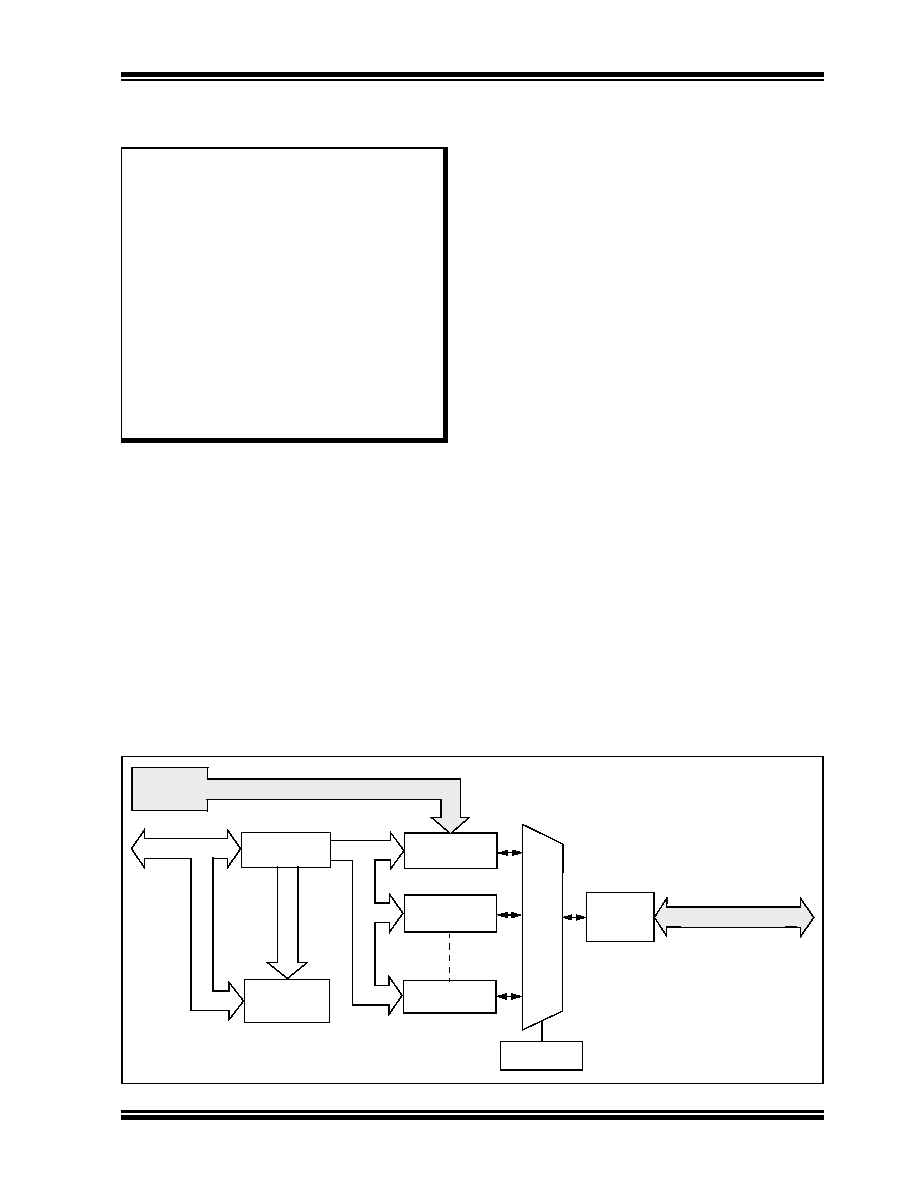

FIGURE 9-1:

DMA BLOCK DIAGRAM

Note 1: This data sheet summarizes the features

of the PIC32MX1XX/2XX family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to Section 31. “Direct

Memory Access (DMA) Controller”

(DS61117)

in

the

“PIC32

Family

Reference Manual”, which is available

(www.microchip.com/PIC32).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

this data sheet for device-specific register

and bit information.

Address Decoder

Channel 0 Control

Channel 1 Control

Channel n Control

Global Control

(DMACON)

Bus Interface

Channel Priority

Arbitration

SEL

SE

L

Y

I0

I1

I2

In

System IRQ

INT Controller

Device Bus + Bus Arbitration

Peripheral Bus

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF46K80-I/ML

MCU PIC ECAN 64KB FLASH 44QFN

AT89S51-24JI

IC 8051 MCU 4K FLASH 44PLCC

AT89S51-24JC

IC 8051 MCU 4K FLASH 44PLCC

AT89S51-24AI

IC 8051 MCU 4K FLASH 44TQFP

AT89S51-24AC

IC 8051 MCU 4K FLASH 44 TQFP

AT89LS52-16PI

IC 8051 MCU FLASH 8K 40DIP

AT89LS52-16PC

IC MCU 8K FLASH LV 16MHZ 40-DIP

AT89LS52-16JI

IC 8051 MCU FLASH 8K 44PLCC

相关代理商/技术参数

PIC32MX130F064D-I/PT

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064D-I/TL

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-I/ML

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-I/PT

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-I/TL

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-V/ML

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-V/PT

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-V/TL

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT